A Homemade SDR Receiver on Zynq

Building an inexpensive HF Web-SDR receiver using a $5 Antminer S9 control board with Zynq SoC, capable of decoding AM, SSB, FT8, WSPR, and more for under $20 in total hardware cost.

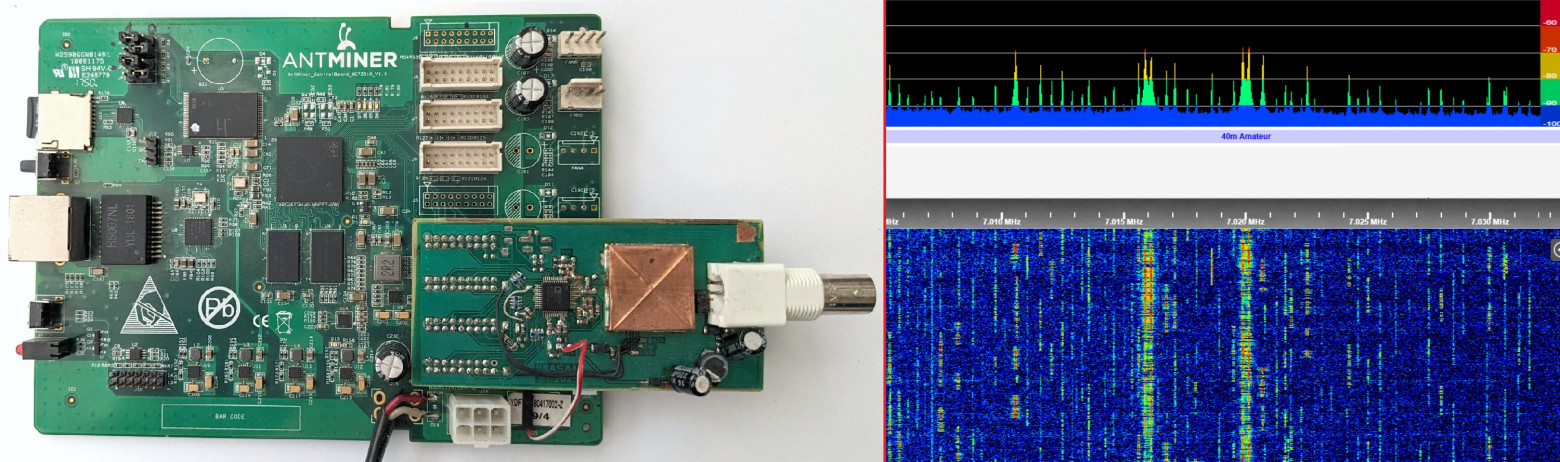

This article describes building an inexpensive HF Web-SDR receiver using the Zynq SoC, based on a used Antminer S9 control board. The project is a fork of the existing WEB-888 receiver, which itself continues the KiwiSDR receiver.

KiwiSDR Background

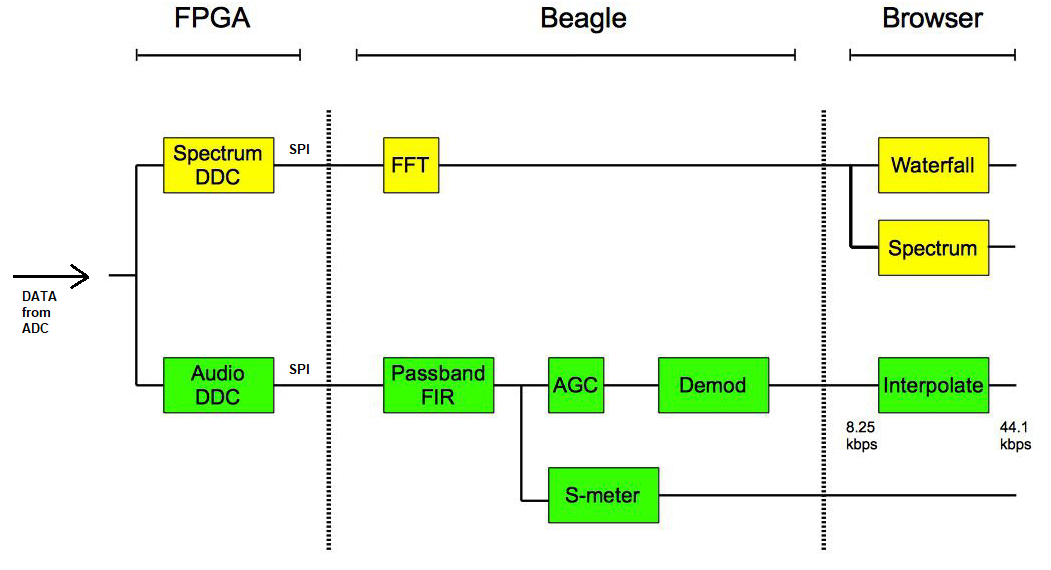

KiwiSDR is an open-source online SDR receiver developed by John Seamons. It uses the DDC (Digital Down Conversion) principle with an LTC2248 ADC at 65 MSPS and a Xilinx Artix-7 FPGA for initial data processing. The receiver gained popularity in the amateur radio community for its ability to share radio spectrum access over the web.

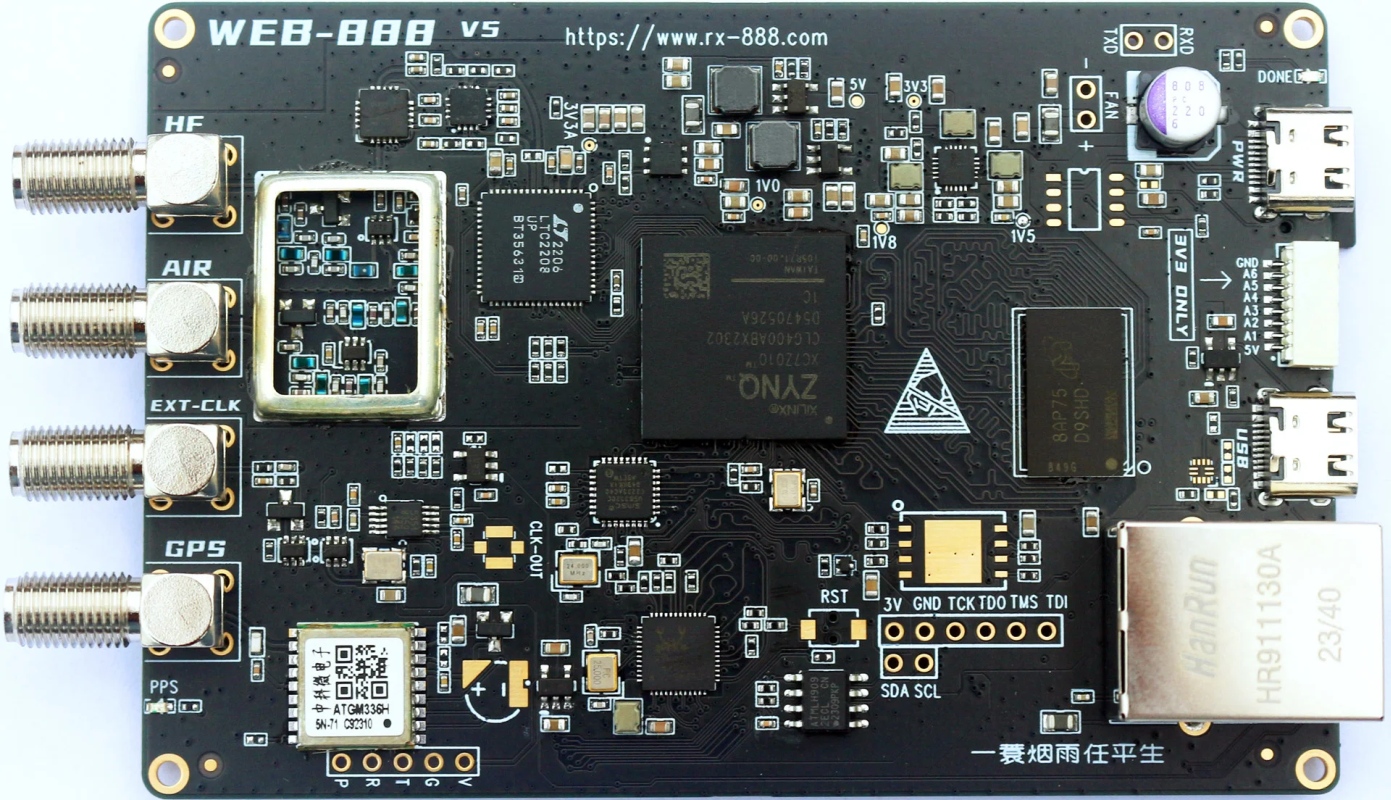

WEB-888 Receiver

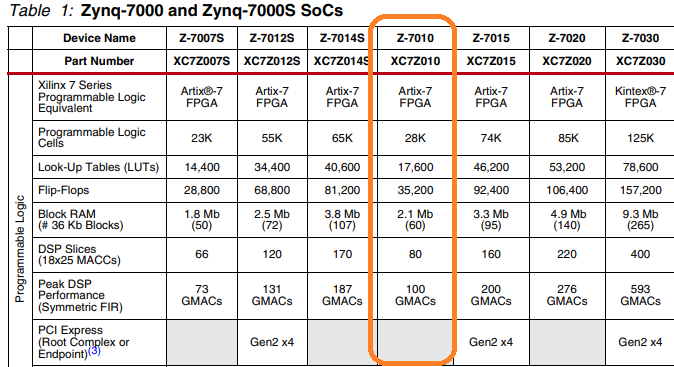

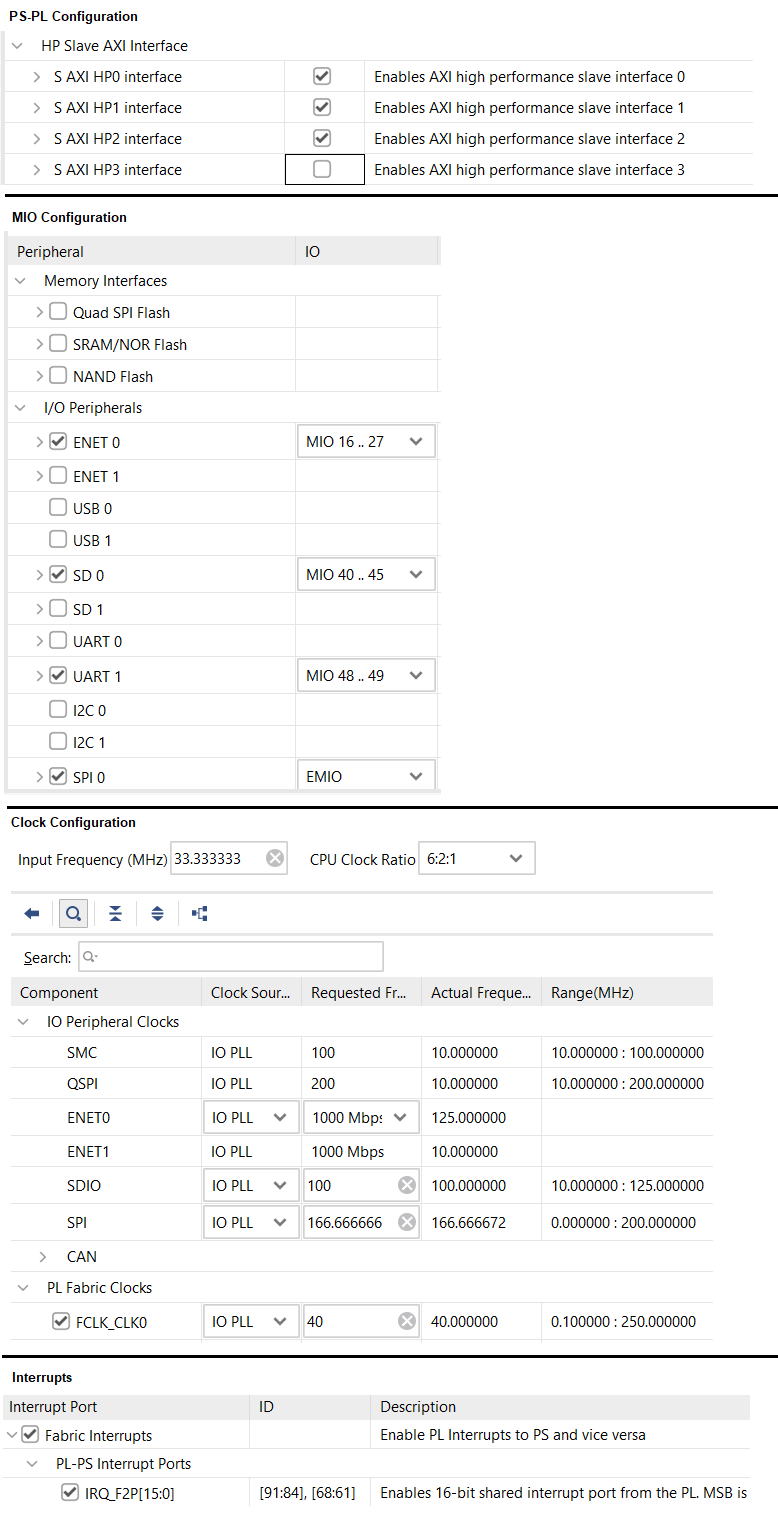

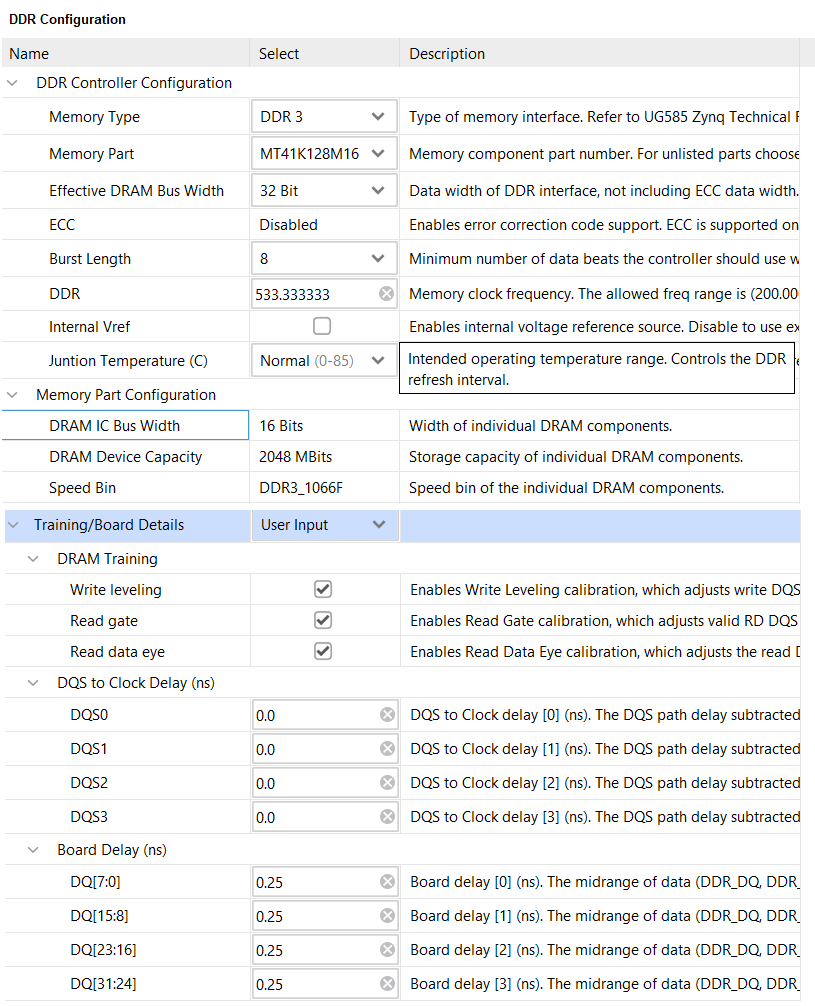

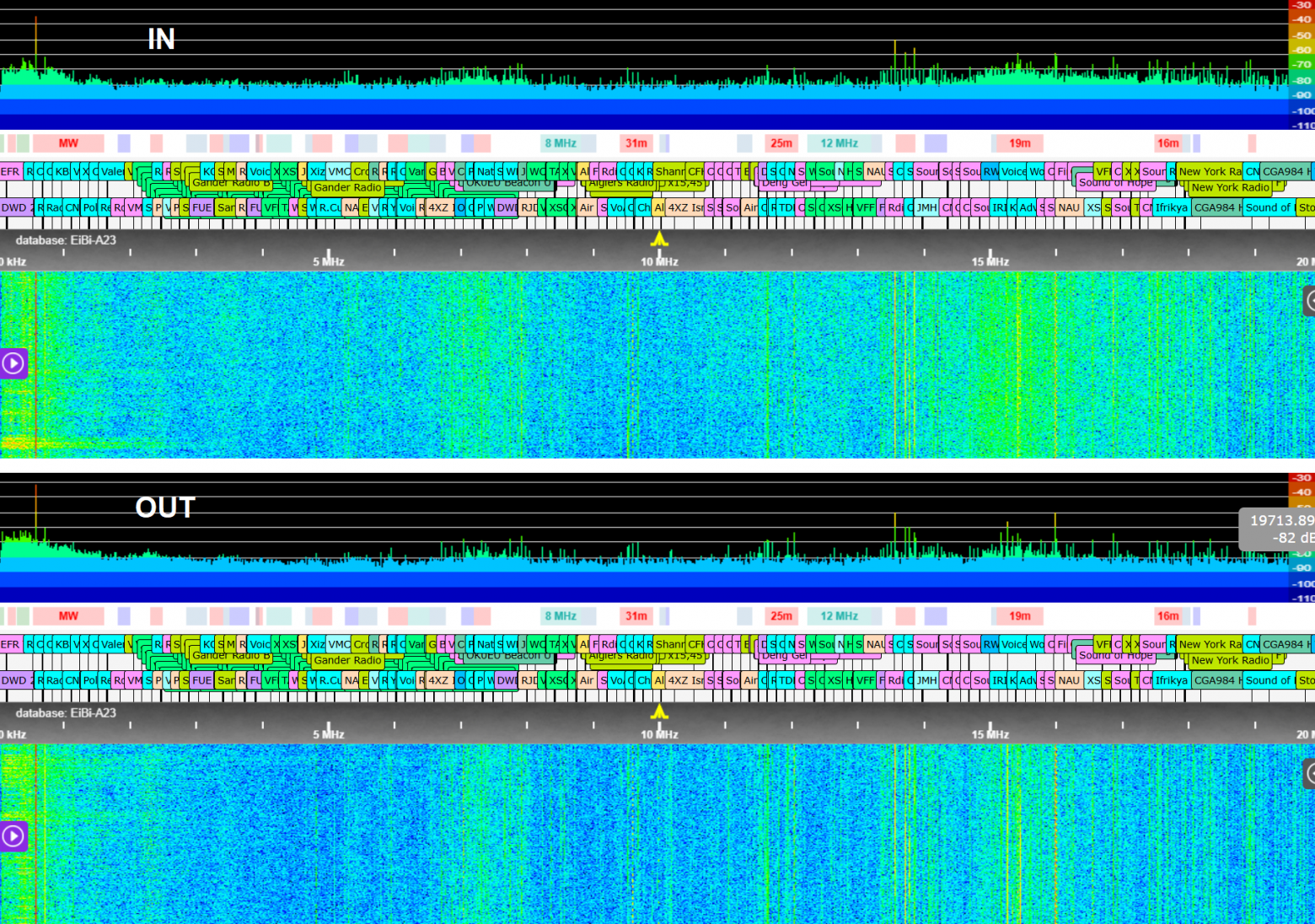

The WEB-888 emerged in 2024, using a Zynq7010 SoC containing a dual-core ARM A9 processor and FPGA. It features an LTC2208 16-bit 130 MSPS ADC with improved specifications over KiwiSDR, offering better dynamic range and wider bandwidth.

The Custom Build

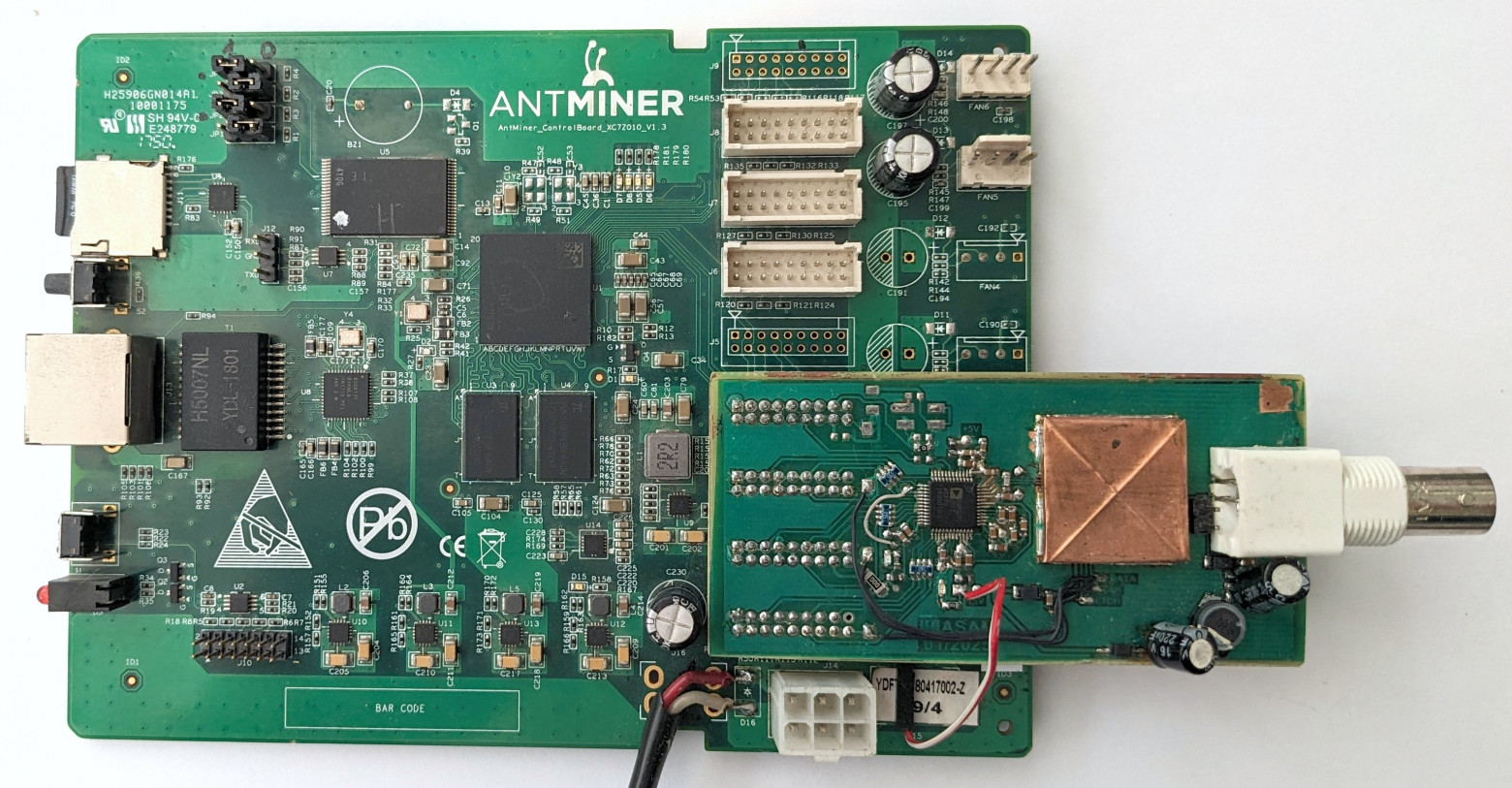

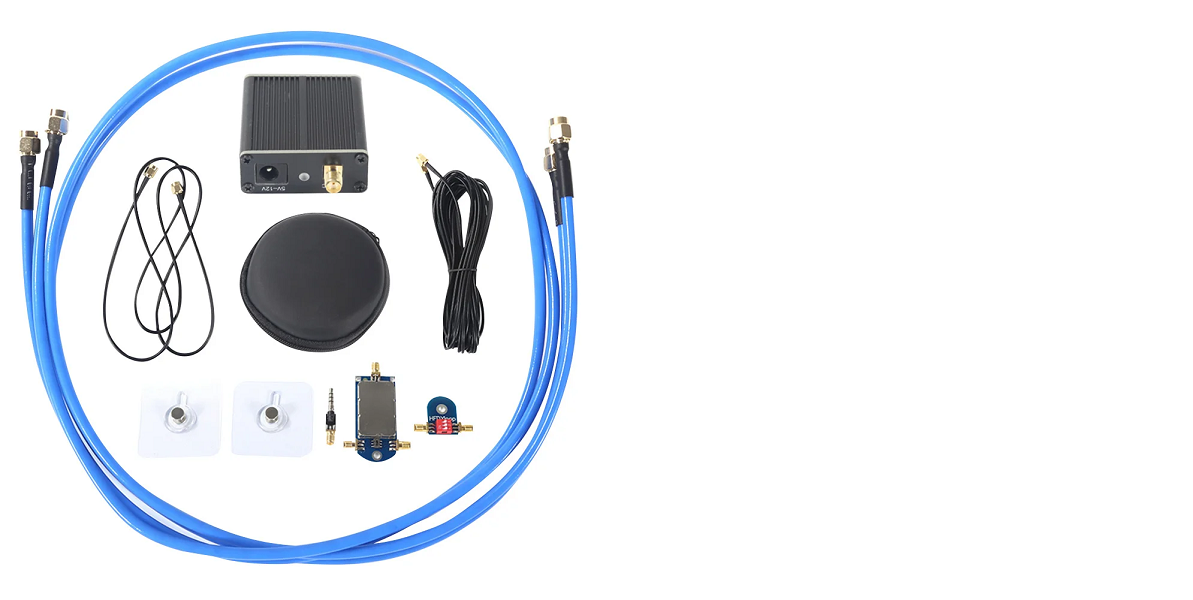

The key advantage of this build is cost. The Antminer S9 control board costs approximately $5 and contains a Zynq7010 with 512MB RAM, NAND flash, SD card slot, and gigabit Ethernet PHY. These boards are readily available as surplus from cryptocurrency mining operations.

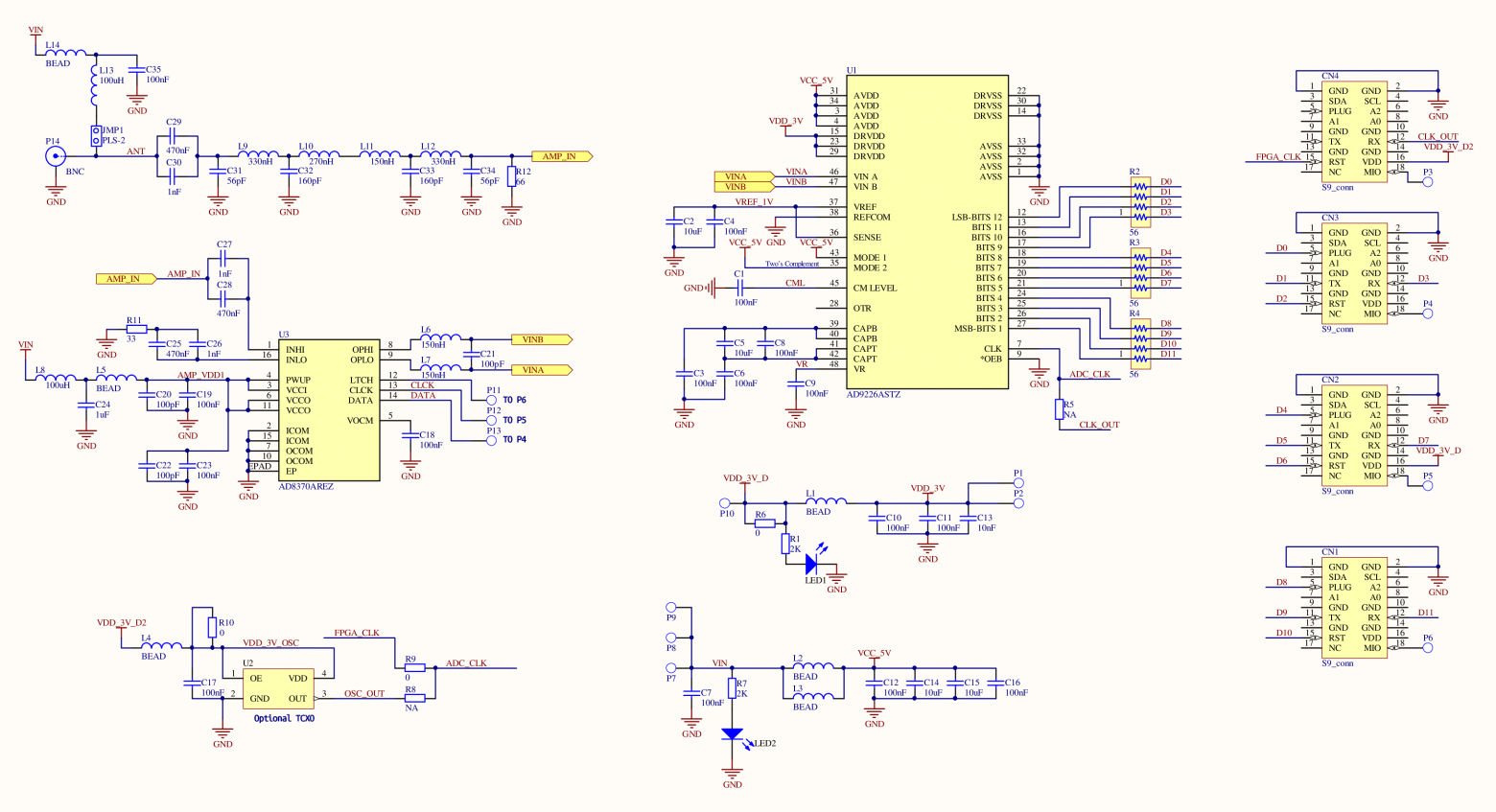

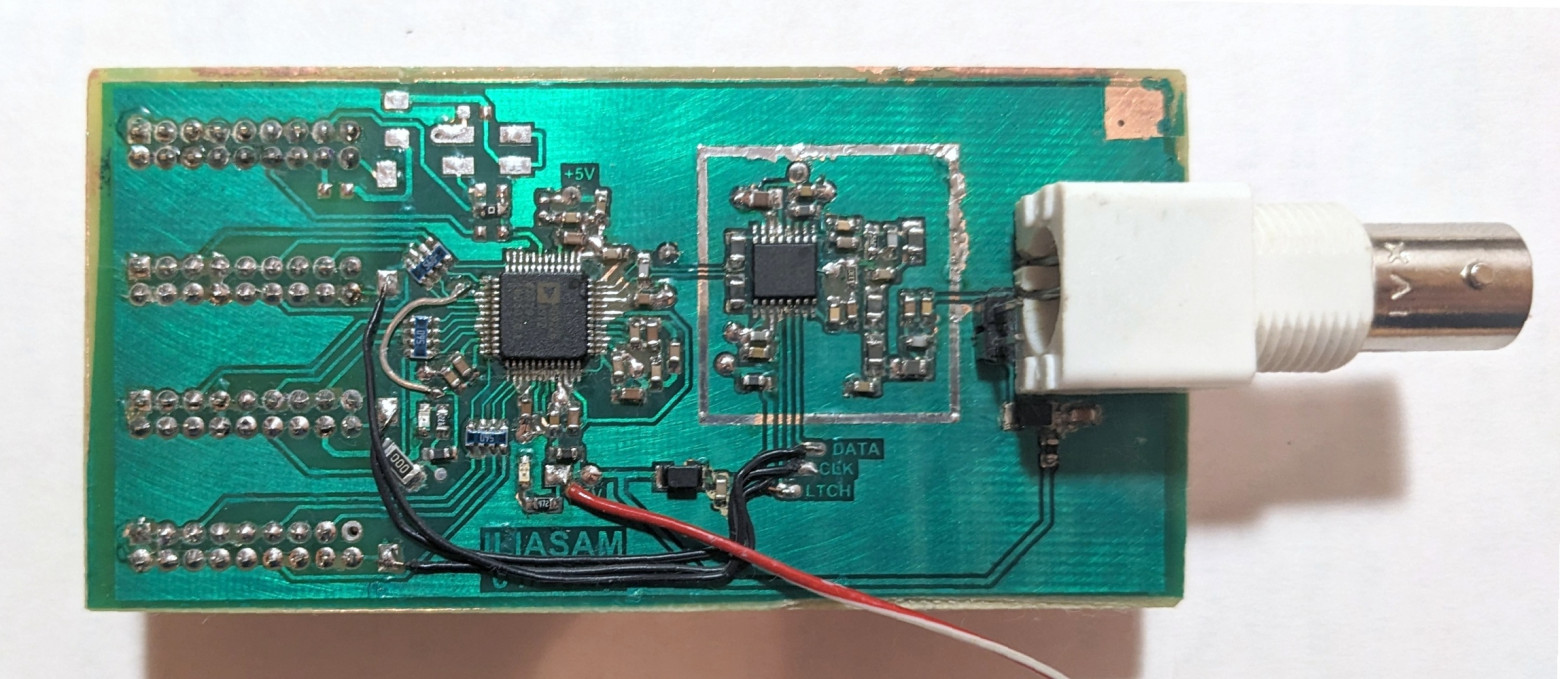

ADC Board Design

The custom receiver uses an AD9226 12-bit 65 MSPS ADC (under $5) with an AD8370 programmable gain amplifier offering -11 to +34 dB gain. A 30 MHz low-pass filter precedes the amplifier to prevent aliasing. The ADC board connects to the Zynq board via a simple ribbon cable.

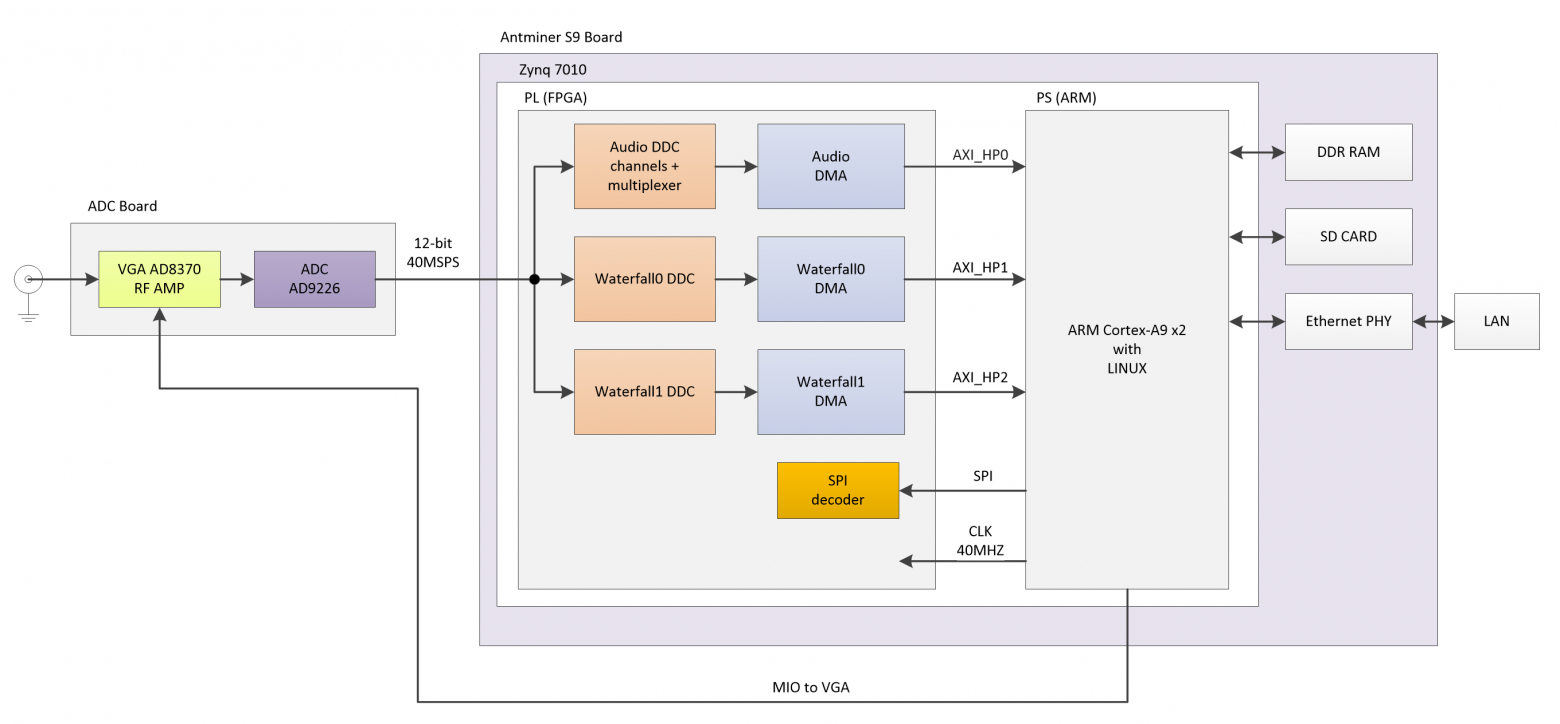

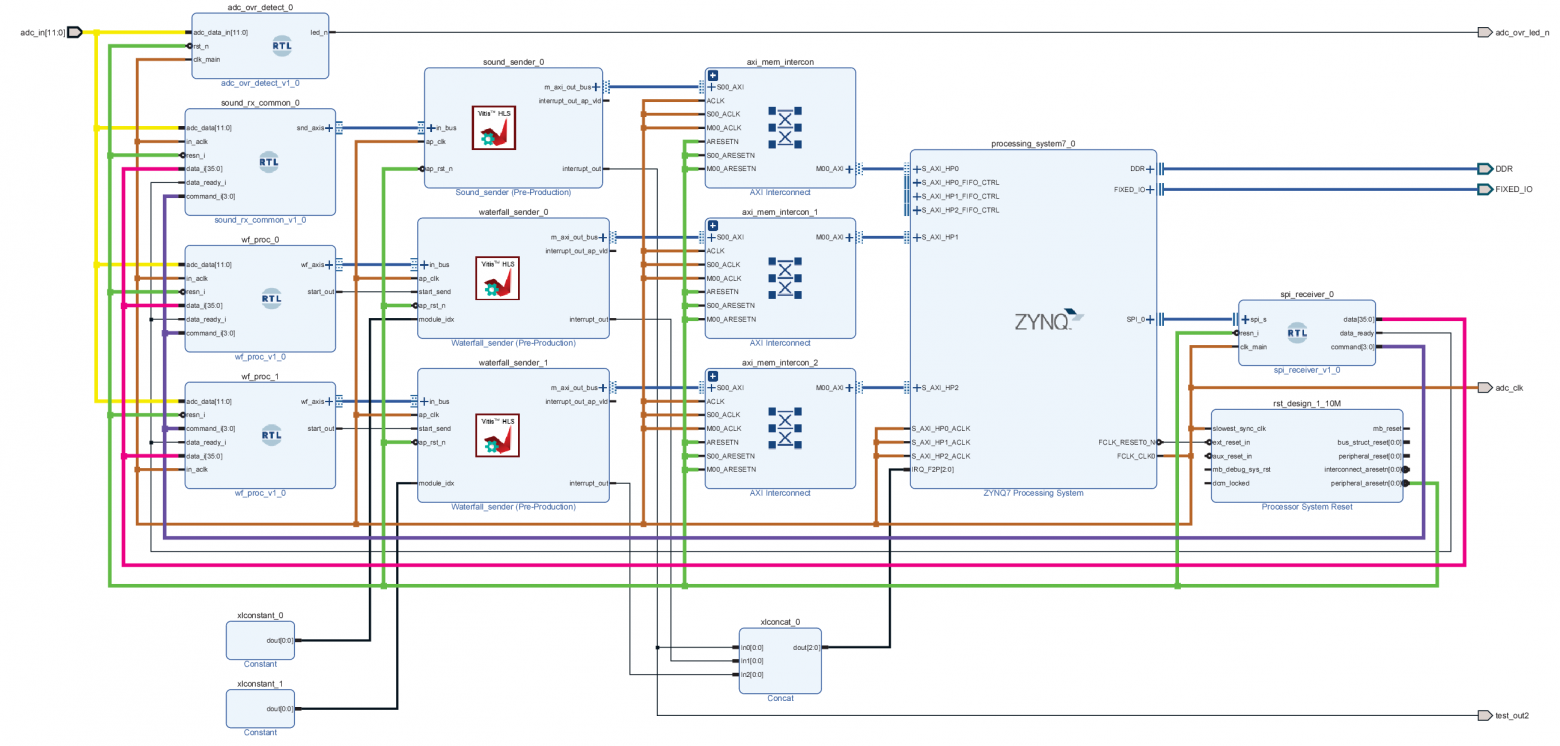

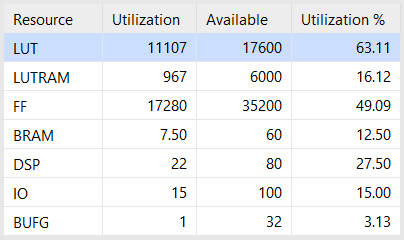

FPGA Implementation

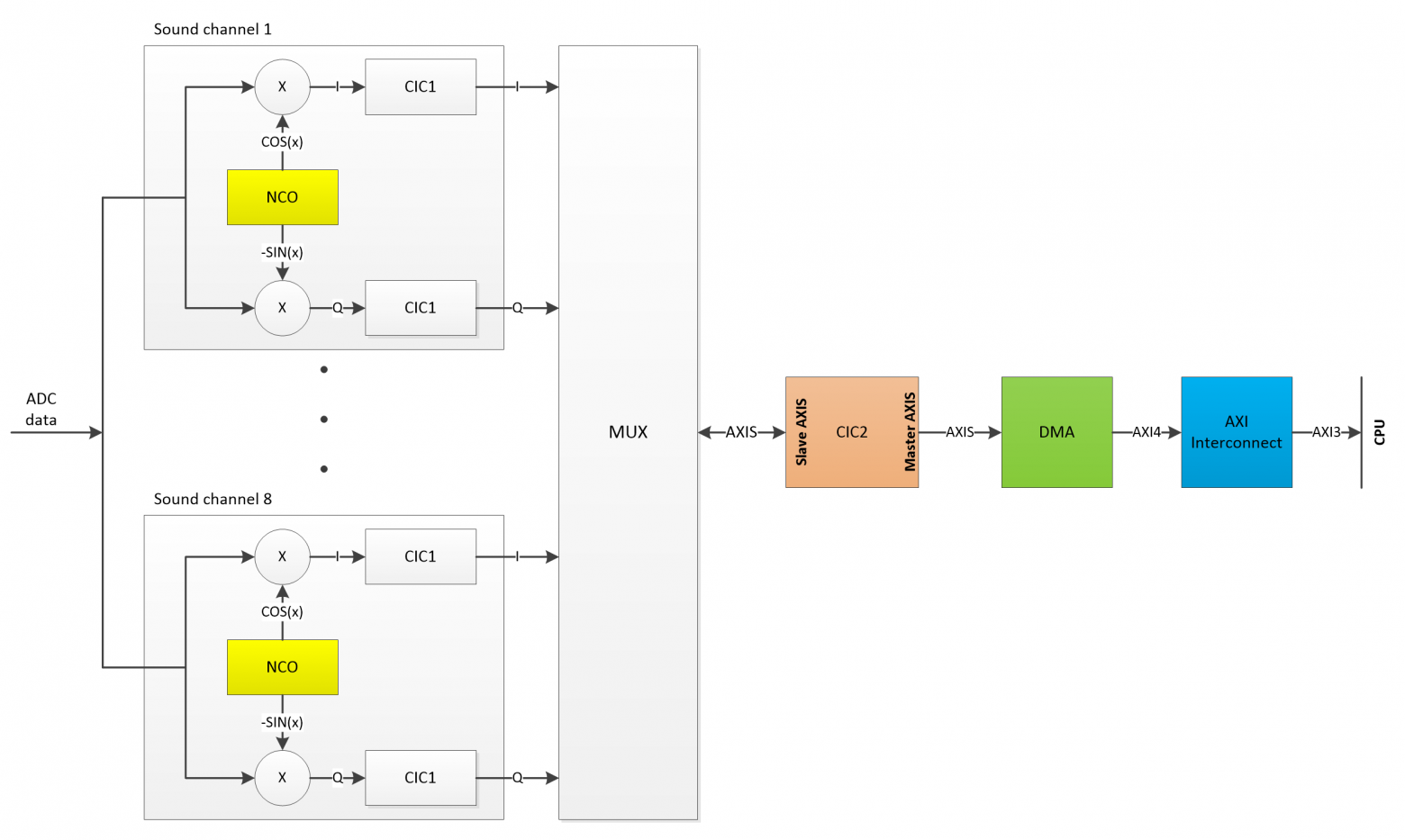

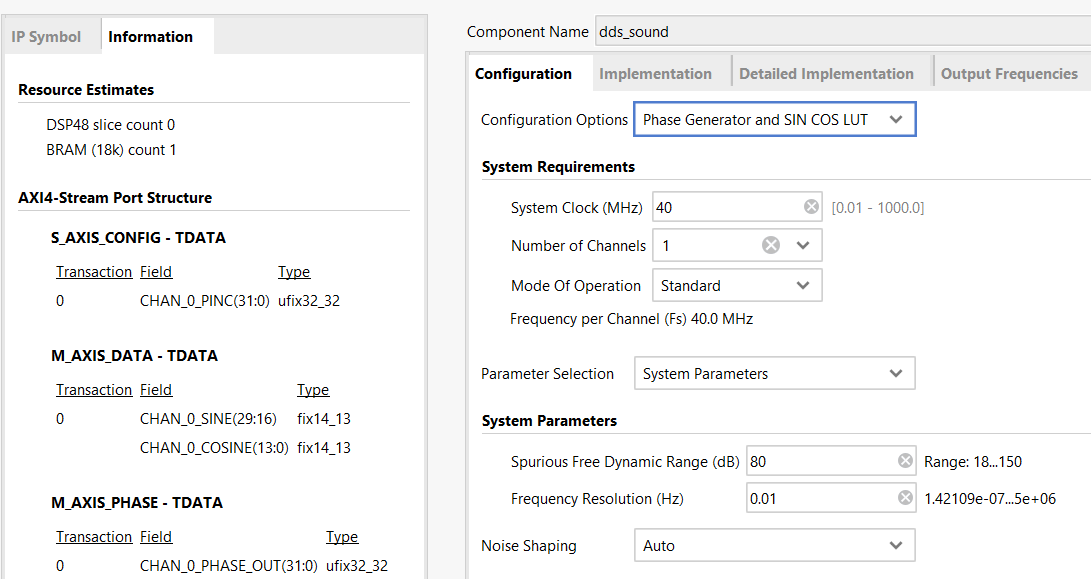

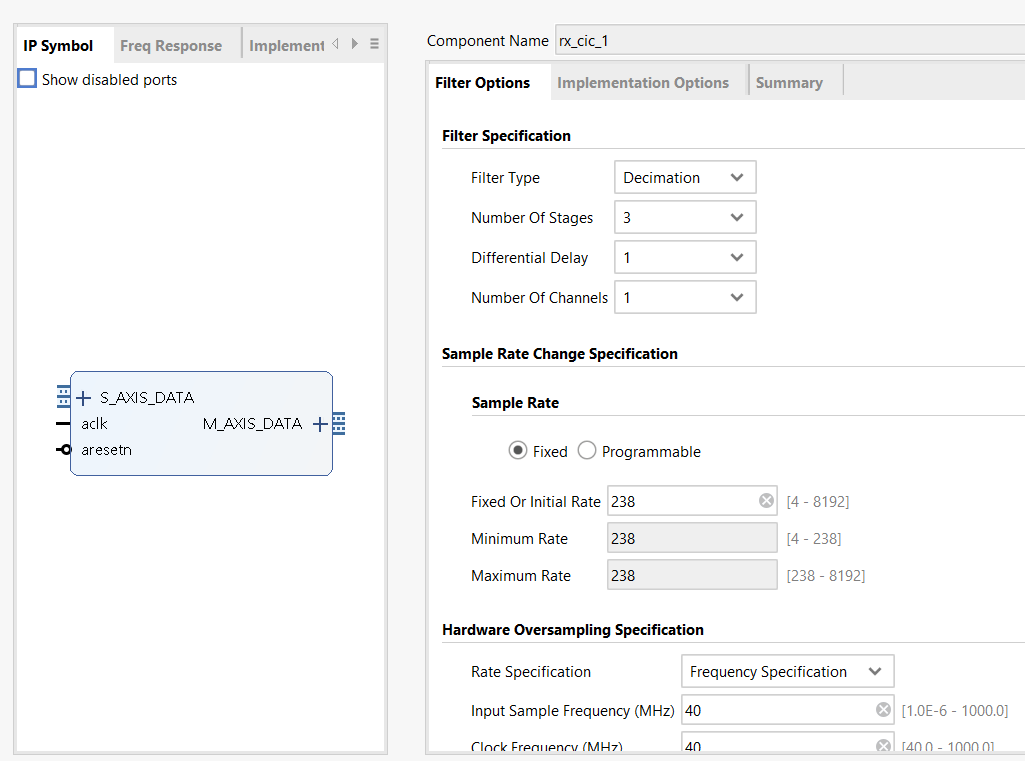

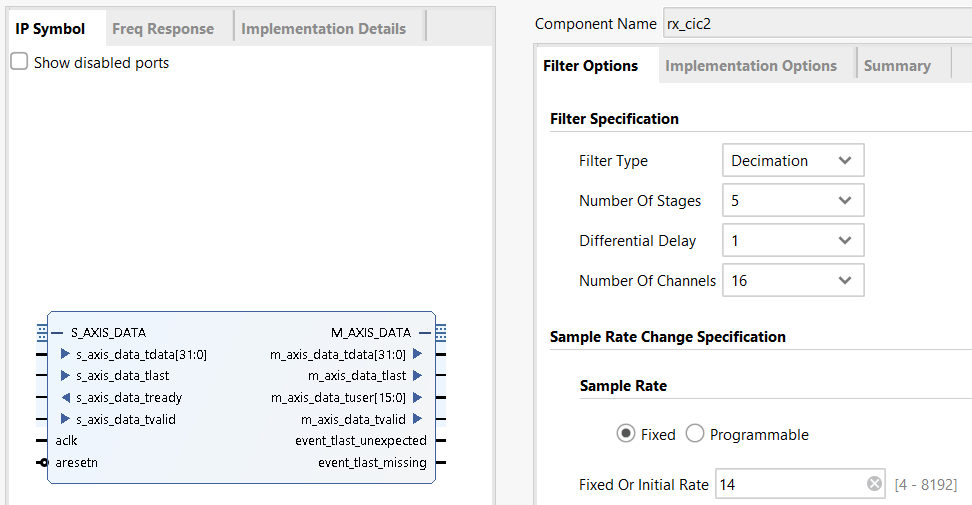

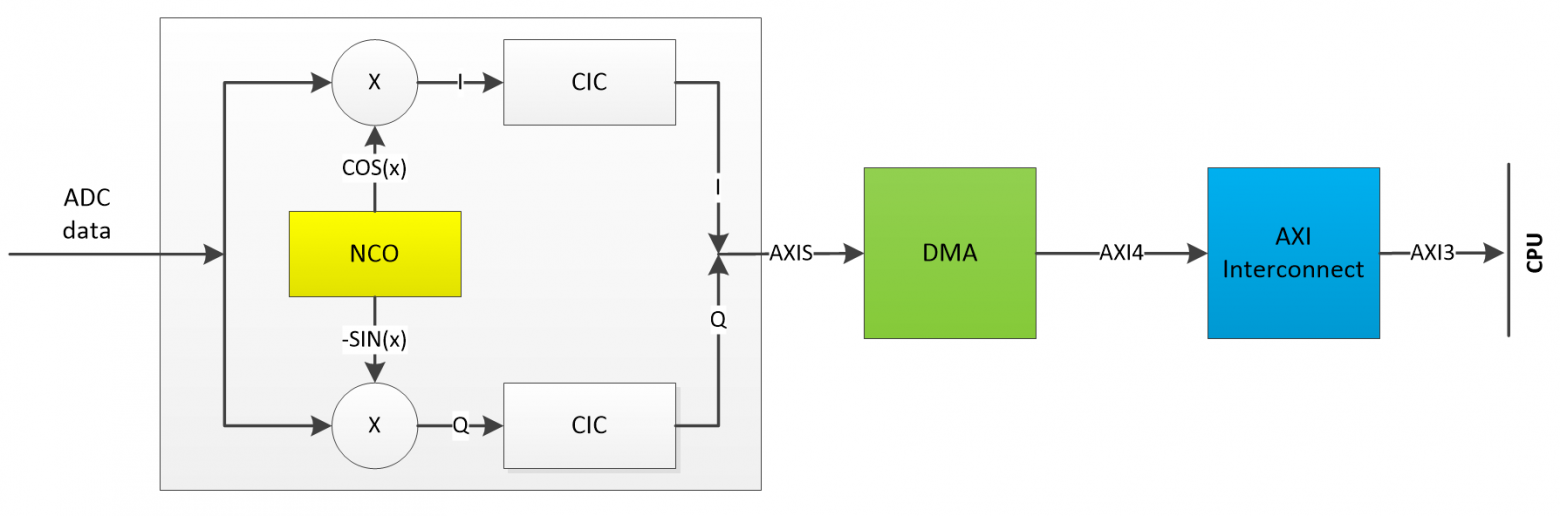

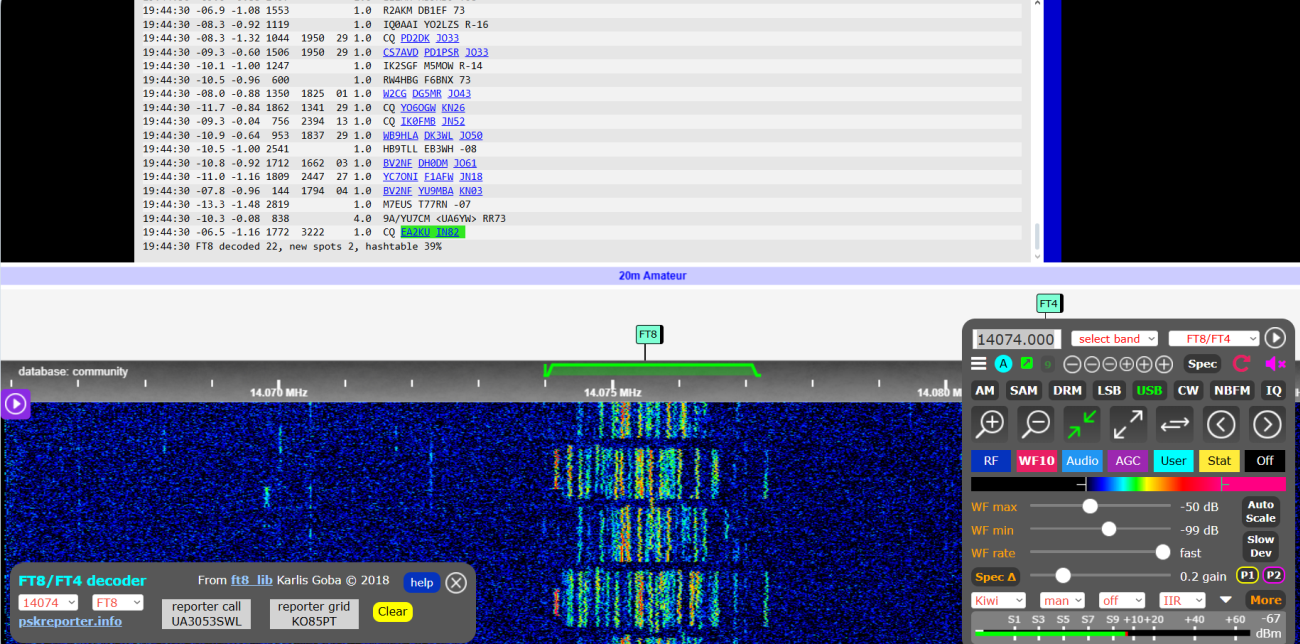

Audio Processing: Eight audio channels are implemented with DDS-based frequency conversion and CIC filtering at a 238x decimation factor, achieving an output sample rate of 12,004.8 Hz. Each channel can be independently tuned to a different frequency within the receiver's bandwidth.

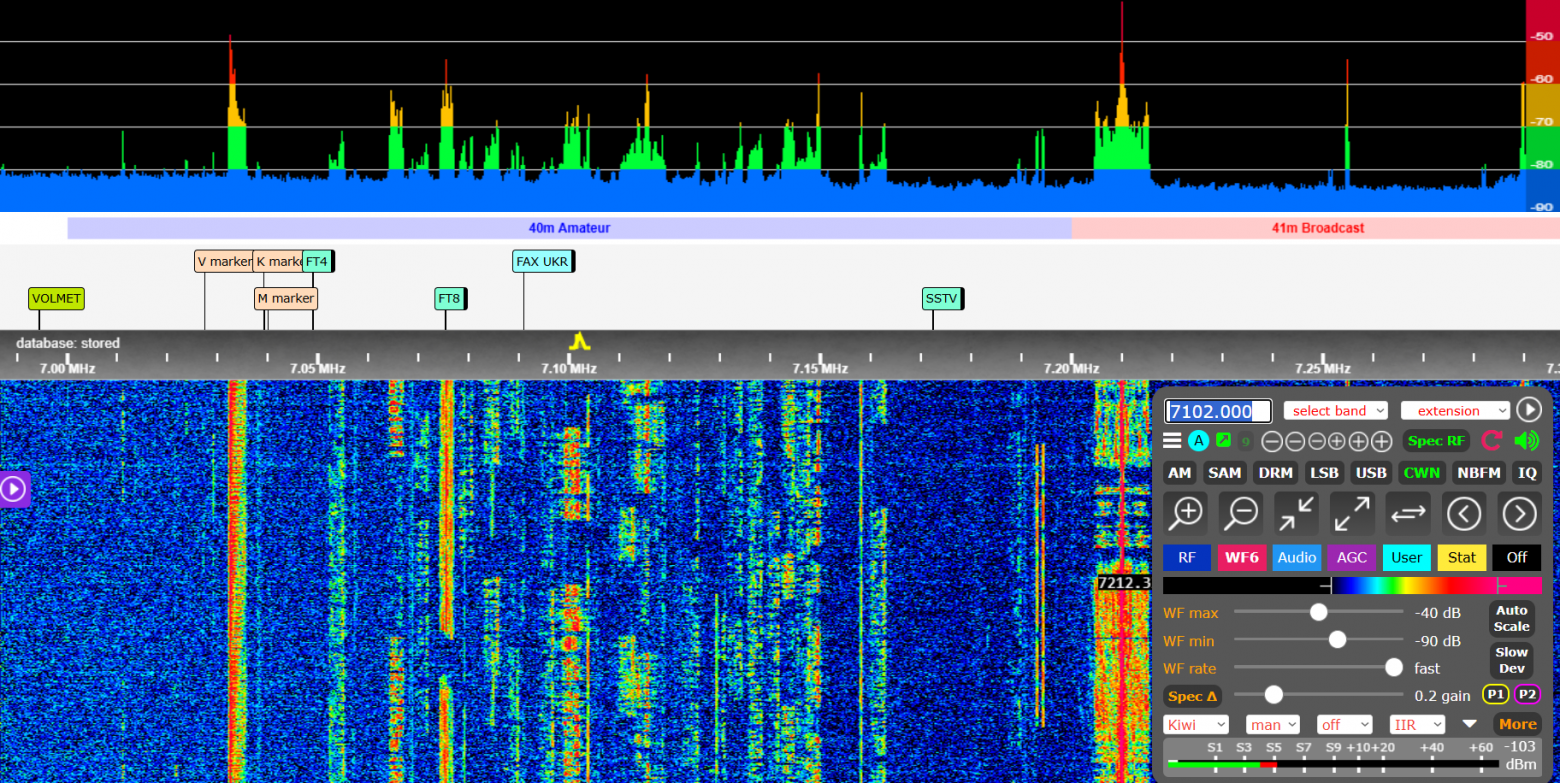

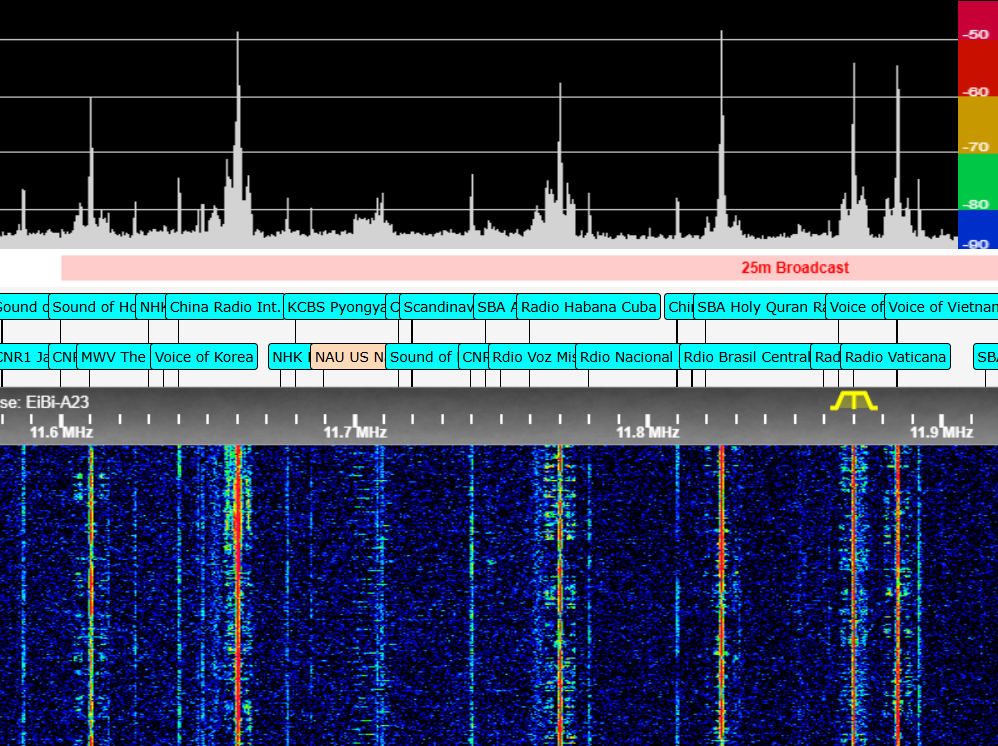

Waterfall Processing: Two waterfall channels use a similar architecture with variable decimation (up to 2^11). These channels generate the spectrum display data that users see in the web interface.

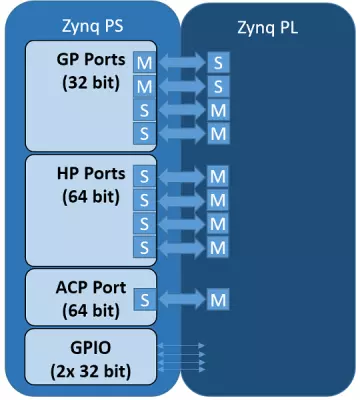

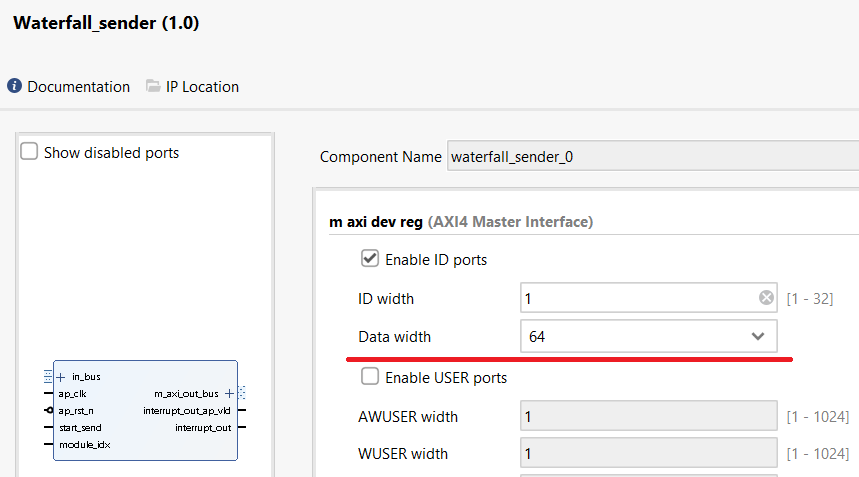

DMA Architecture: Custom DMA modules were created using Vitis HLS, transferring data to PS RAM via AXI HP interfaces. This allows efficient data movement between the FPGA fabric and the ARM processor without consuming excessive CPU cycles.

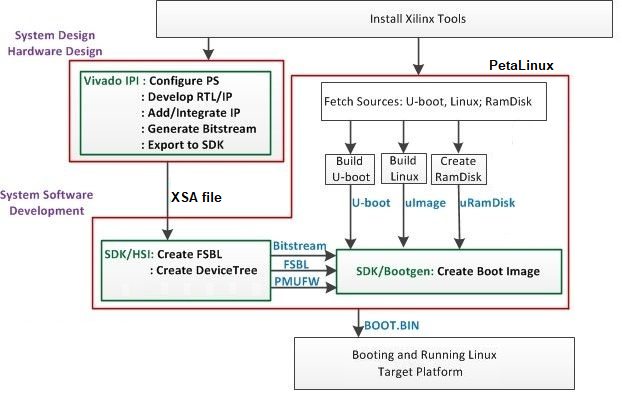

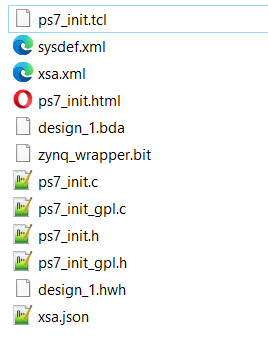

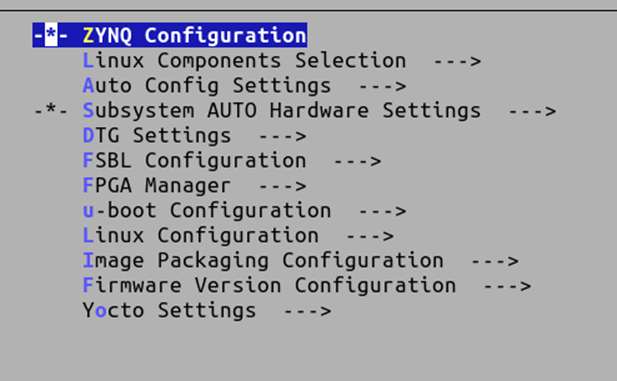

Linux and Software Stack

PetaLinux: Used for building Linux, bootloader, and device tree configuration. The Zynq boots from the SD card, loading the FPGA bitstream and Linux kernel.

Kernel Module: A custom loadable kernel module handles DMA interrupts and data buffering through FIFO. It provides a character device interface that the userspace application reads from.

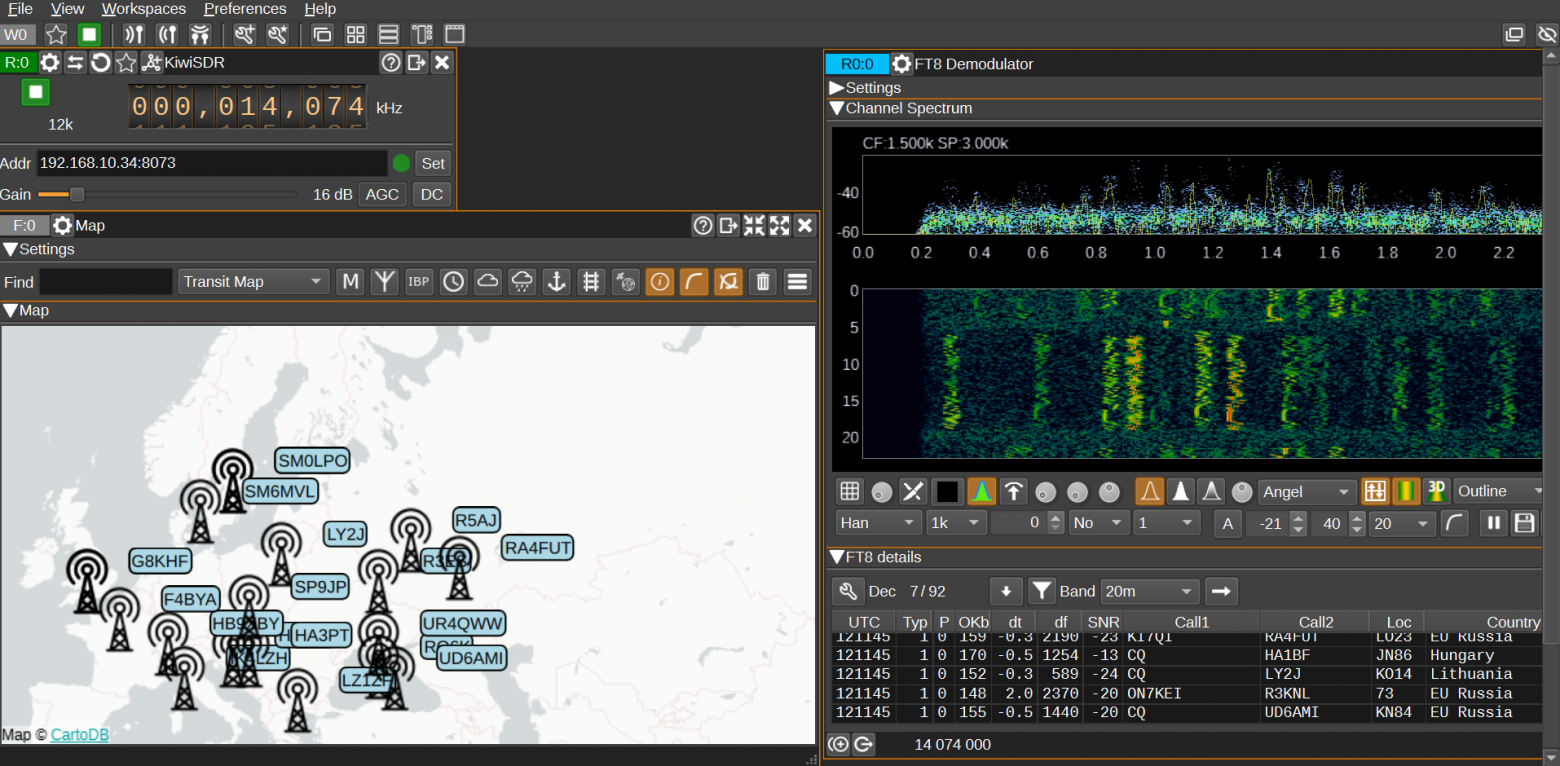

Application: A modified WEB-888 server application with custom FPGA interface code, adapted for Ubuntu compatibility. The web interface allows remote users to tune frequencies, select demodulation modes, and view the waterfall display.

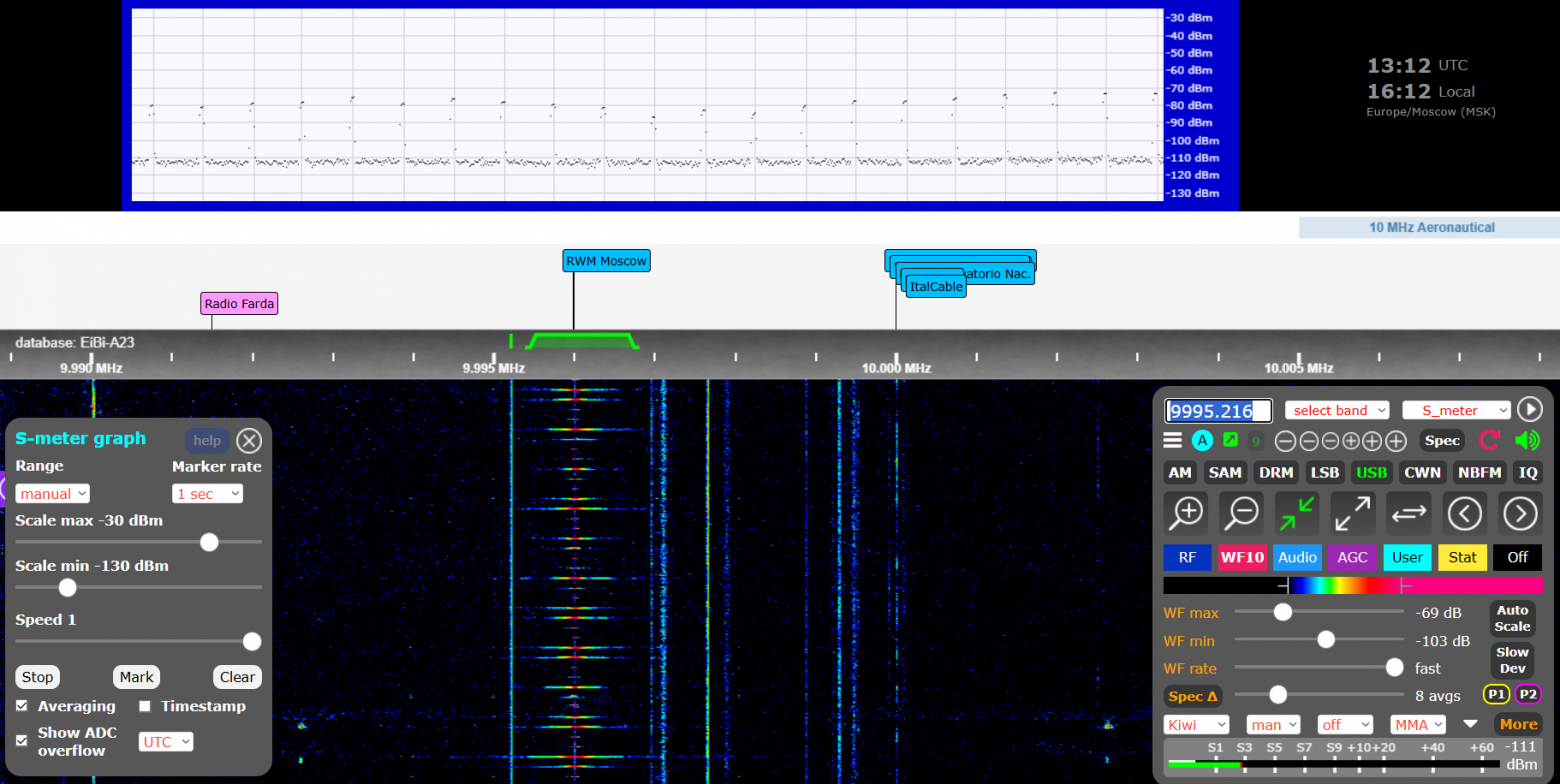

Reception Capabilities

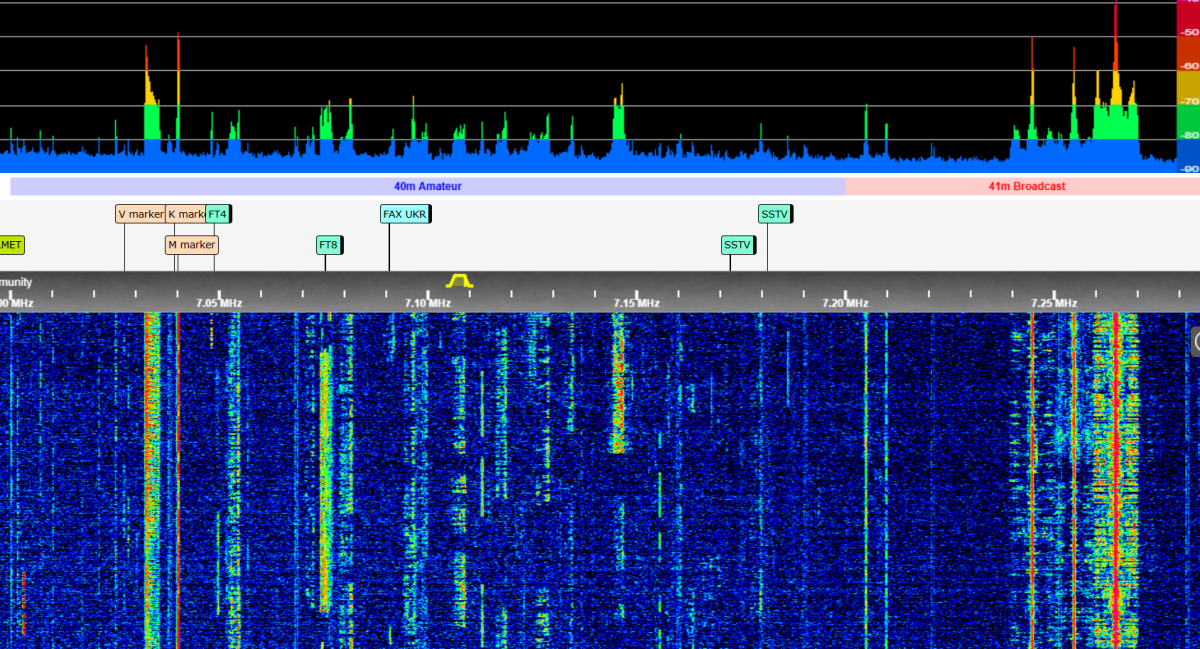

The receiver was successfully tested decoding a wide variety of signals:

- Standard AM/SSB broadcast stations

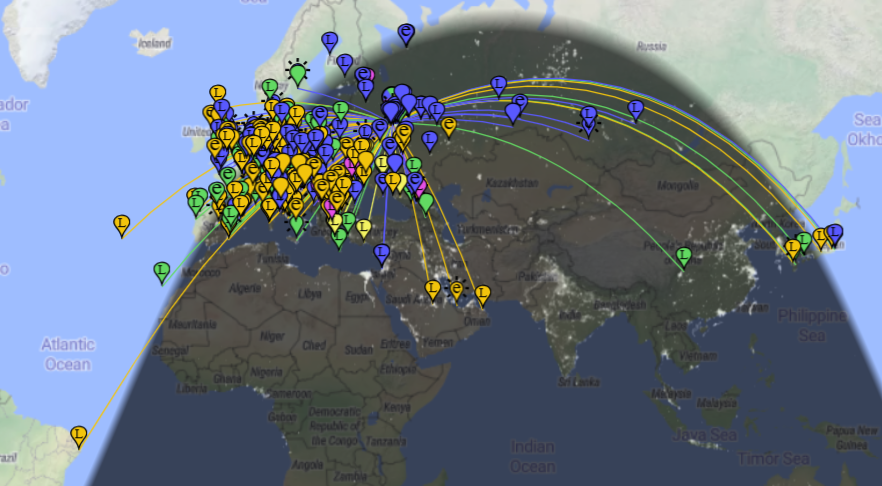

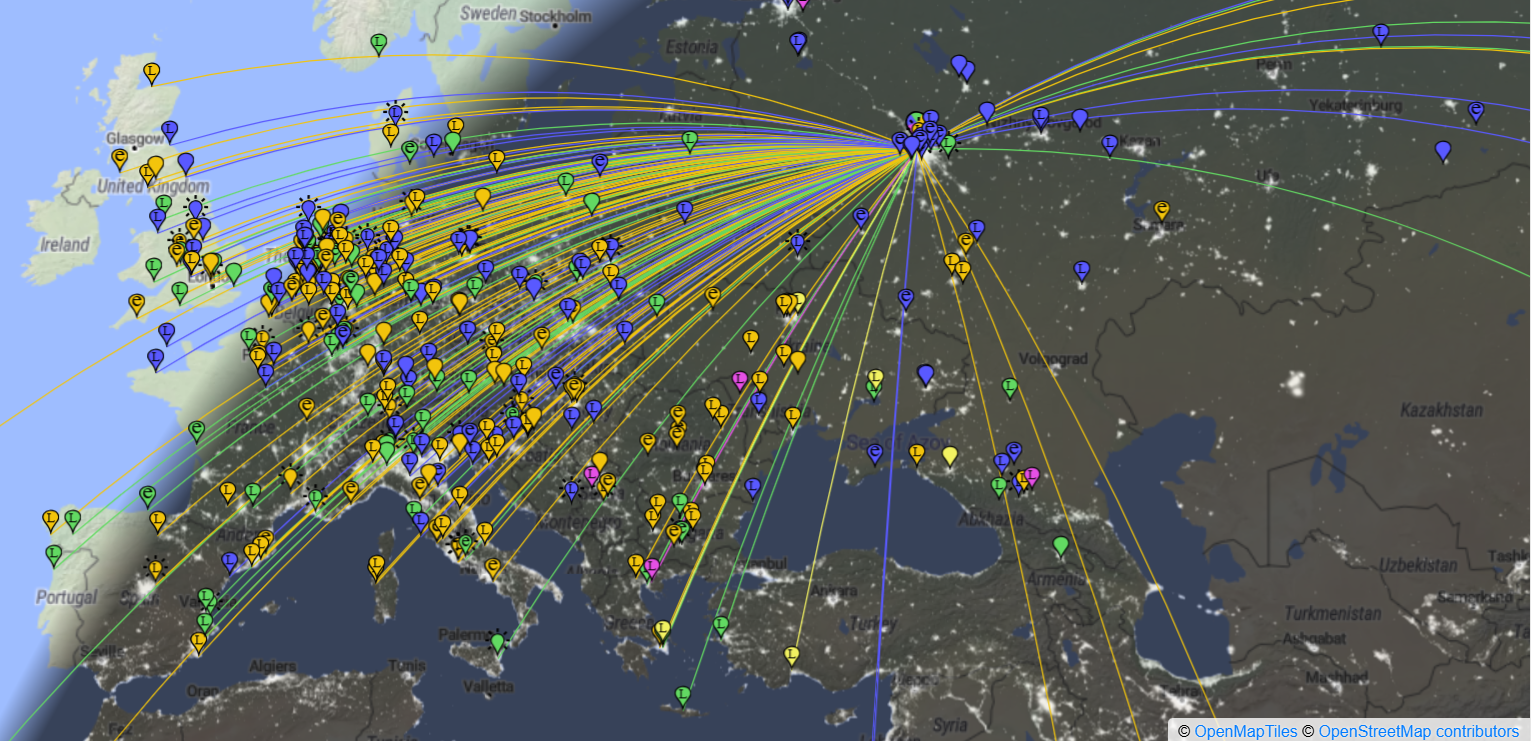

- FT8/FT4 amateur radio digital modes

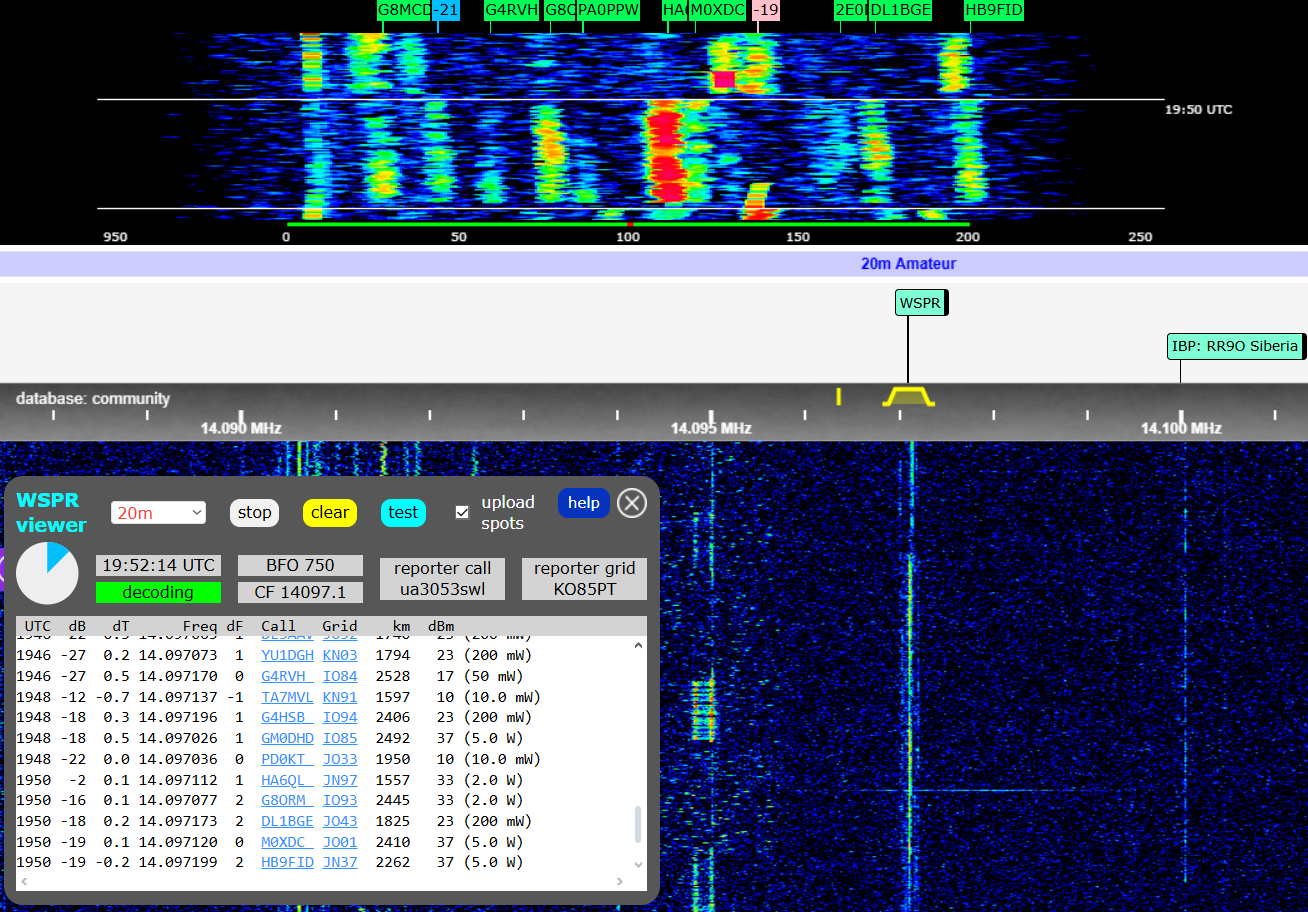

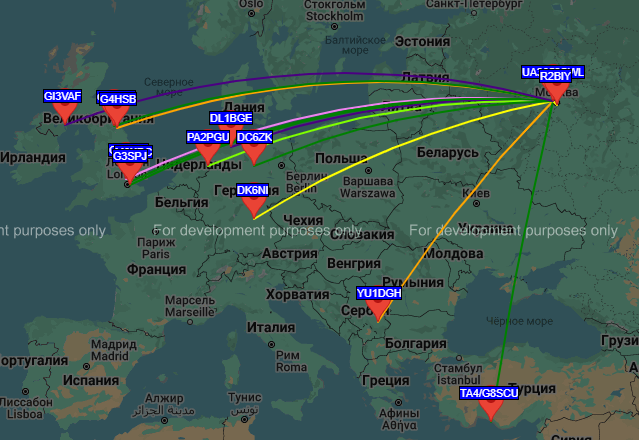

- WSPR beacon signals

- Radioteletype (RTTY)

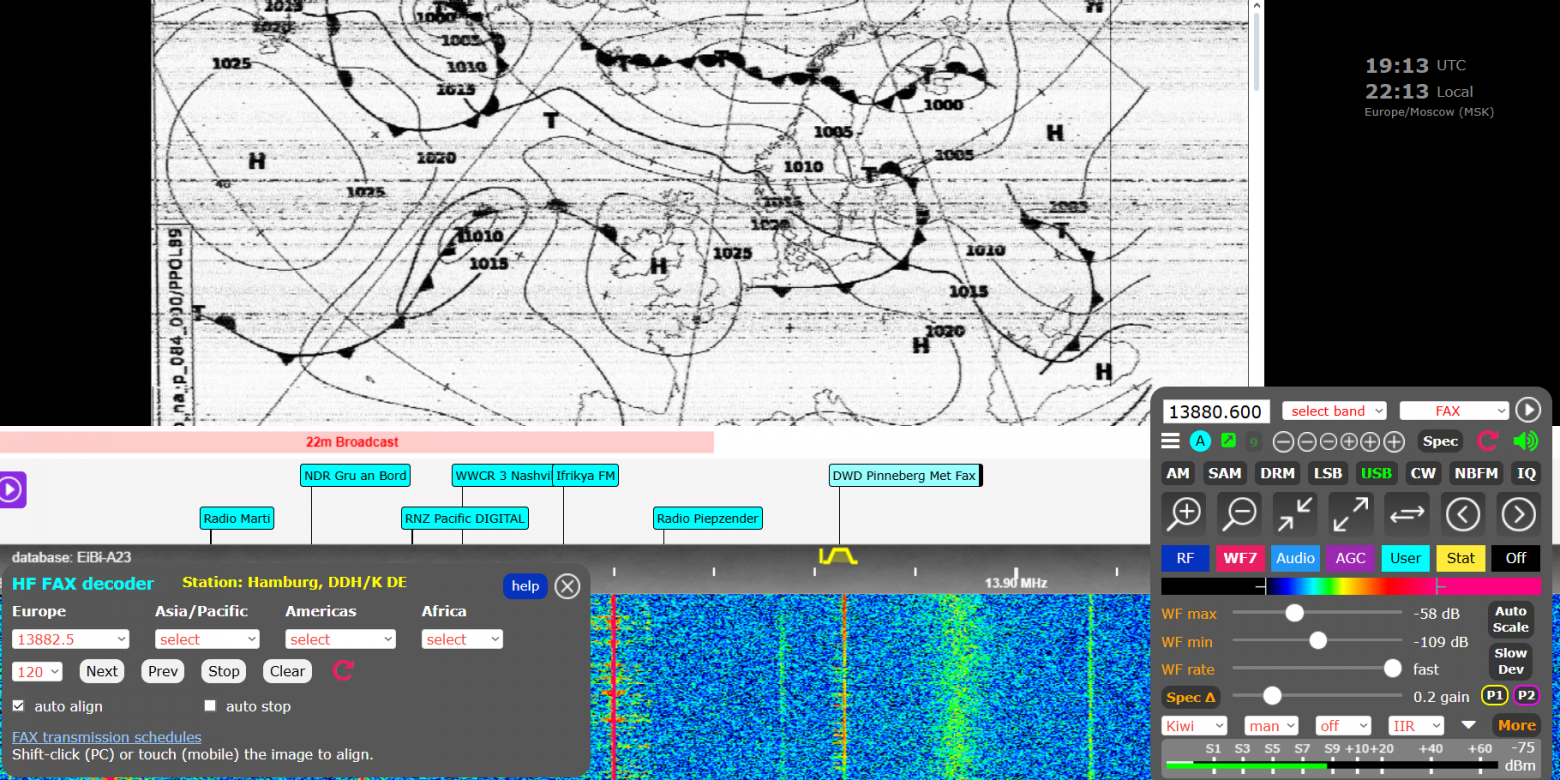

- Weather fax imagery

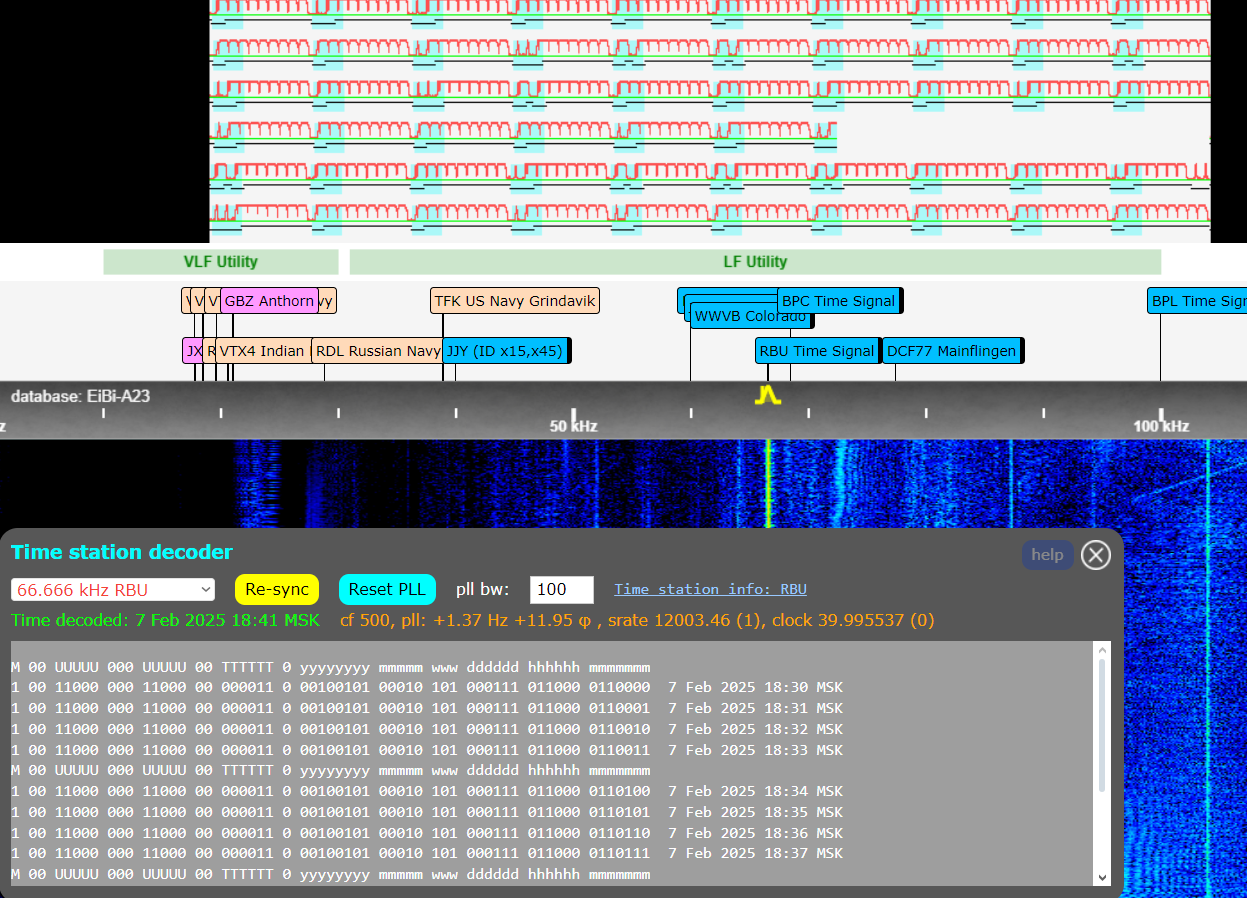

- Time station signals (RBU, DCF77)

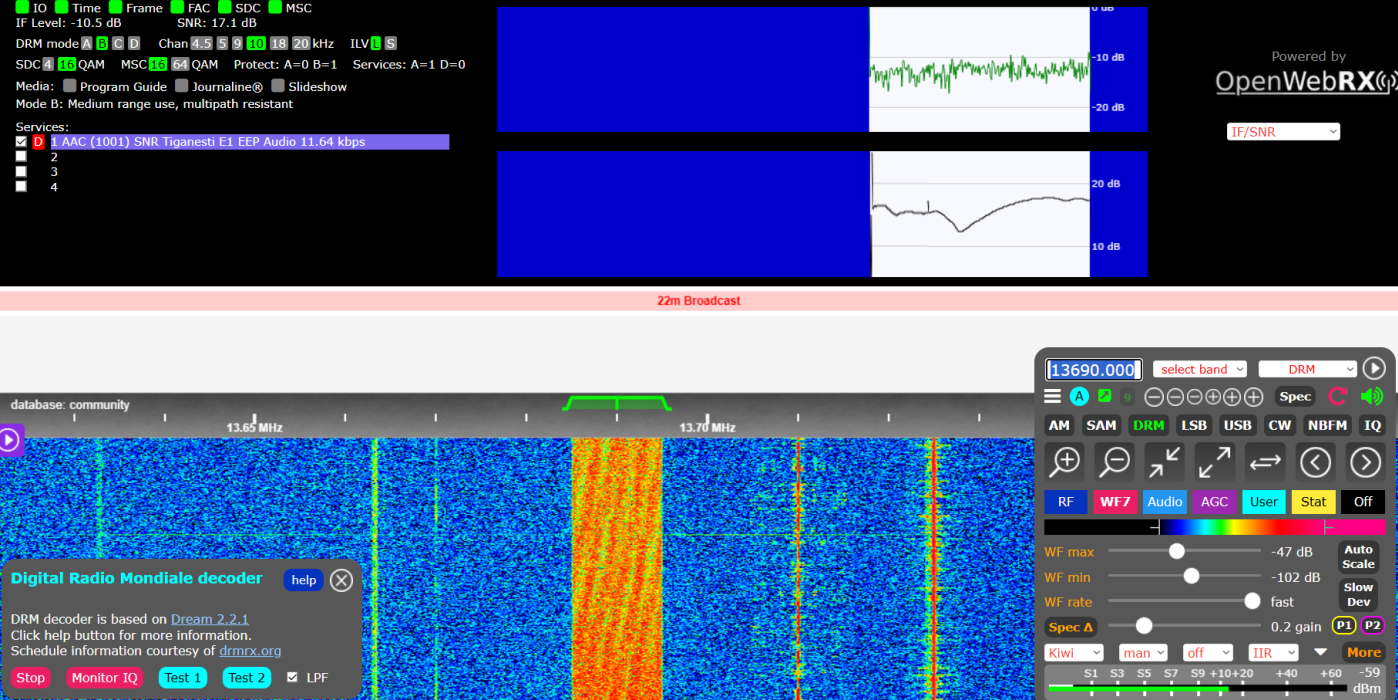

- DRM digital radio broadcasts

Project Cost and Repositories

Total receiver cost: around $15-20 for hardware (excluding antenna and enclosure). This makes it one of the most affordable Web-SDR receivers available.

The project is open source:

- Hardware designs: https://github.com/iliasam/OpenZynqSDR_HW

- Software and kernel driver: https://github.com/iliasam/OpenZynqSDRApp

FAQ

What is this article about in one sentence?

This article explains the core idea in practical terms and focuses on what you can apply in real work.

Who is this article for?

It is written for engineers, technical leaders, and curious readers who want a clear, implementation-focused explanation.

What should I read next?

Use the related articles below to continue with closely connected topics and concrete examples.